SOLUTION

ケイデンスの設計ソリューション、TSMC-SoIC™ 先進3Dパッケージング技術への対応を発表

2019.4.24 1:44 pm

TSMC SoICパッケージング技術向けに最適化されたケイデンスのデジタル設計、サインオフ、カスタム/アナログ設計、ICパッケージおよびPCB解析に対応する包括的なツールソリューション

ケイデンス・デザイン・システムズ社(本社:米国カリフォルニア州サンノゼ市、以下、ケイデンス)は、4月23日(米国現地時間)、TSMCが、ロジックICやメモリーを含め、異なるプロセスノードで製造されたヘテロジニアスなチップを1つのパッケージに統合する新しいTSMCの System-on-Integrated-Chips (SoIC™) 先進3Dチップ積層技術向けに、ケイデンスの設計ソリューションを認証したことを発表しました。

TSMCのSoICチップ積層技術向けに最適化されたケイデンスのデジタル設計、サインオフ、カスタム/アナログ設計、ICパッケージおよびPCB解析に対応する包括的なツールソリューションにより、ヘテロジニアスなチップセットの統合機能を必要とするお客様は、複雑なデザインを効率的に開発することが可能になります。

TSMC SoIC先進パッケージング技術に対応するケイデンスソリューションに関する詳細については、www.cadence.com/go/soicをご参照ください。

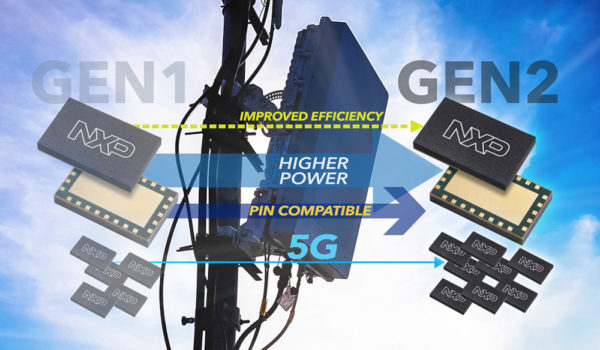

TSMCの革新的なマルチ・チップ積層技術であるSoIC技術は、TSMCの3D IC Wafer-on-Wafer (WoW) およびChip-on-Wafer (CoW) 技術をさらに拡張し、5G、AI、IoT、車載アプリケーションなどの新しいアプリケーションにおける様々な設計要件に対応します。TSMCとケイデンスは、ツール、メソドロジー、フローを共同で改善し、共通のお客様が全体のデザインサイクルの一環としてチップ統合ソリューションにおけるコネクティビティおよび検証を管理するための環境を提供します。全体のデザインサイクルは、3D機能をサポートする複数のツールを連携させることで実現が可能になります。

本フローには、Innovus™ Implementation System、Quantus™ Extraction Solution、Voltus™ IC Power Integrity Solution、Tempus™ Timing Signoff Solution、Physical Verification System (PVS)、 Virtuoso® custom IC design platform、SiP Layout、OrbitIO™ interconnect designer、Sigrity™ PowerSI® 3D-EM Extraction Option、Sigrity PowerDC™ technology、Sigrity XcitePI™ Extraction、Sigrity XtractIM™ technology、Sigrity SystemSI™ technologyが含まれます。

TSMC社コメント

Suk Lee氏(Senior director, Design Infrastructure Marketing Division):

「TSMCの新しいSoIC先進チップ積層技術に対応するケイデンスツール、リファレンスフロー、メソドロジーは、実績のあるTSMCのInFO、 WoW、CoWoSチップ統合ソリューションを補完するものであり、3D積層技術を使用して1つのデバイス上に複数ダイを統合する柔軟なソリューションをお客様に提供します。現在も継続している先進パッケージング技術におけるTSMCとケイデンスの協業は、両社共通のお客様の5G、AI、IoT、車載アプリケーション向け製品設計を効率化し、成功に導くお手伝いをします。」

ケイデンス コメント

Tom Beckley(Senior vice president and general manager, Custom IC & PCB Group):

「ケイデンスとTSMCは長年にわたり協業しており、新しい先進SoIC チップ積層技術に対応する革新的な機能を実現した今日においても続いています。このSoICソリューションにより、お客様は、最適化されたツール、フロー、メソドロジーを使用した最新の3D技術を採用し、設計開発の厳しいスケジュールに間に合わせることが可能となります。」

■日本ケイデンス・デザイン・システムズ社

http://www.cadence.co.jp